TOP

TOP

CoAsia SEMI (CEO DS Shin) announced that it has begun supplying SoC products utilizing 3D IC packaging, effectively expanding its business domain into the 3D IC packaging ecosystem. This marks the first successful case of 3D IC packaging within the Korean design service industry.

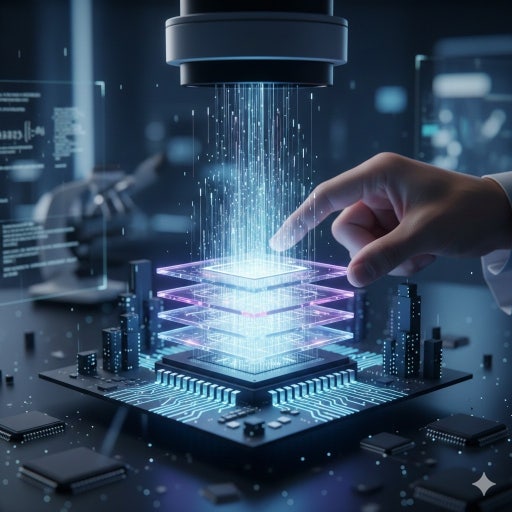

The 3D IC packaging featured in this product employs TSV (Through-Silicon Via) technology to vertically stack customized DRAM and SoCs. Compared to traditional 2D and 2.5D packaging, this structure shortens signal transmission paths and increases bandwidth, simultaneously enhancing performance, power efficiency, and integration density. As a technology requiring advanced design and verification expertise, its application is expected to grow rapidly in high-performance computing sectors such as AI, data centers, and autonomous driving.

CoAsia SEMI started delivering products this month for customer certification and testing, with plans to enter full-scale mass production within the year. Specific details regarding the client and contract remain confidential due to trade secret protection requirements.

DS Shin, CEO of CoAsia SEMI, stated, "This supply is the direct result of our proactive investment in next-generation 3D IC technology, moving beyond existing fields like HBM and advanced packaging." He further emphasized, "By being the first among domestic design houses to meet export compliance standards and obtain export approvals amidst global semiconductor regulations, we have secured a solid business foundation for unrestricted collaboration with overseas customers, including those in China."